# SCL4015B

DUAL FOUR STAGE SHIFT REGISTER

PROPAGATION DELAY TIME

**RESET PULSE WIDTH**

**RESET REMOVAL TIME**

MINIMUM

<sup>t</sup>PHL

PWR

trem

5

10

15

5

10

15

5

10

15

### STATIC CHARACTERISTICS: ( $V_{SS} = 0 V$ )

| PARAMETER        | CONDITIONS                           | V <sub>DD</sub><br>(Vdc) | W*<br>MAX | MIN | + 25°C<br>TYP |    | T <sub>HI</sub> | GH**<br>MAX | UNIT |

|------------------|--------------------------------------|--------------------------|-----------|-----|---------------|----|-----------------|-------------|------|

| QUIESCENT DEVICE | $V_{IN} = V_{SS} \text{ or } V_{DD}$ | 5                        | 5         |     | 0.05          | 5  |                 | 150         |      |

| CURRENT IDD      |                                      | 10                       | 10        |     | 0.1           | 10 |                 | 300         | µAdc |

|                  |                                      | 15                       | 15        |     | 0.2           | 20 |                 | 600         |      |

Note:  $T_{LOW} = -55^{\circ}C$  for C / H devices, -40°C for E / S devices,  $*T_{HIGH} = +125^{\circ}C$  for C / H devices, +85°C for E / S devices.

## DYNAMIC CHARACTERISTICS: ( CL = 50pF, TA = 25°C )

| PARAMETER                                  | V <sub>DD</sub> | MINIMUM | TYPICAL | MAXIMUM  | UNIT |

|--------------------------------------------|-----------------|---------|---------|----------|------|

|                                            | Vdc             |         |         |          |      |

| PROPAGATION DELAY                          | 5               |         | 250     | 500      |      |

| TIME <sup>t</sup> PLH, <sup>t</sup> PHL    | 10              |         | 100     | 200      | ns   |

|                                            | 15              |         | 90      | 180      |      |

| OUTPUT TRANSITION                          | 5               | 1       | 100     | 200      |      |

| TIME <sup>t</sup> TLH, <sup>t</sup> THL    | 10              |         | 50      | 100      | ns   |

|                                            | 15              |         | 40      | 80       |      |

| CLOCK PULSE WIDTH                          | 5               |         | 200     | 400      |      |

| MINIMUM PW <sub>CL</sub>                   | 10              |         | 100     | 200      | ns   |

|                                            | 15              |         | 80      | 160      |      |

| CLOCK FREQUENCY                            | 5               | 1.25    | 2.5     |          |      |

| MAXIMUM f <sub>CL</sub>                    | 10              | 2.5     | 5       |          | MHz  |

|                                            | 15              | 3       | 6       |          |      |

| CLOCK RISE & FALL TIME                     | 5               | 15      |         |          |      |

| MAXIMUM <sup>t</sup> rCL, <sup>t</sup> fCL | 10              | 15      |         |          | μs   |

|                                            | 15              | 5       |         |          |      |

| DATA INPUT/SETUP TIME                      | 5               |         | 150     | 300      |      |

| MINIMUM t <sub>set</sub>                   | 10              |         | 50      | 100      | ns   |

|                                            | 15              |         | 40      | 80       |      |

| DATA INPUT HOLD TIME                       | 5               |         | 0       | 50       |      |

| MINIMUM <sup>t</sup> hold                  | 10              |         | 0       | 25       | ns   |

|                                            | 15              |         | 0       | 15       |      |

| RESET OPERATIONS                           |                 |         |         | <u> </u> |      |

#### **CONNECT DIAGRAM**

VDD D8 88 018 028 038 04A CLA

| 16 | 15 | 14 | 18 | 12 | -11 | ,10 | 9 |

|----|----|----|----|----|-----|-----|---|

| 1  | 2  | 3  | 4  | 5  | 6   | 7   | 8 |

CLB Q48 Q3A Q2A Q1A RA DA VSS

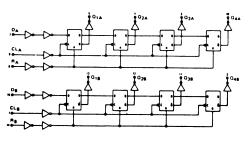

### LOGIC DIAGRAM

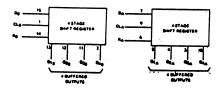

#### **BLOCK DIAGRAM**

## DIE DRAWING

SCL4015B 70 x 70 mils

Note: Refer to "SCL4000B SERIES FAMILY SPECIFICATIONS" for remaining Dynamic & Static Characteristics, and, for recommended and maximum operating conditions.

This datasheet has been downloaded from http://www.digchip.com at this page

200

100

90

200

80

60

375

125

100

400

200

180

400

160

120

750

250

200

ns

ns

ns